https://youtu.be/ivuxlA_twww

< 디램 시장의 Z >

우리는 이 Z에 대한 이야기를 이미 계속해서 접하고 있는 중입니다.

이제 128단까지 쌓아 올린 낸드플래시 시장에서 말입니다.

하지만 반도체 시장의 Z는 단지 낸드플래시만의 것은 아닙니다.

D램 시장에도 이제 Z에 대한 이야기가 시작되는 중입니다.

"패키징을 통해 디램을 적층 시킨다"

이 문장으로 혹시 떠올리시는 단어가 있으신가요?

어떤 분들께 이제 너무도 익숙해진 단어일지도 모를 이 HBM이

메모리 시장의 또 다른 Z의 모습이 되겠습니다.

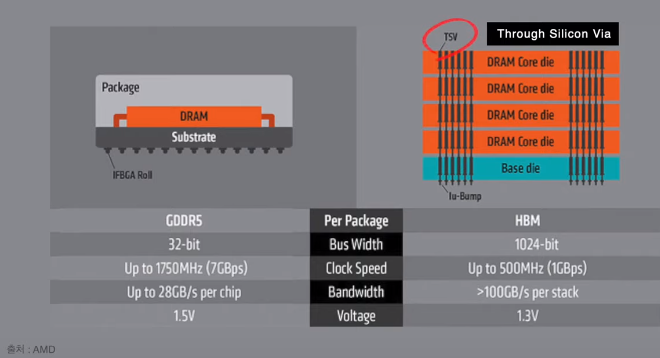

기존의 사용하던 일반 D램은 PCB 기판의 이 D램칩들이

이렇게 가로로 정렬되어 있는 구조입니다.

HBM에서는 이렇게 D램칩들이 수직으로 적층 되어있습니다.

이러한 HBM의 구조를 실현하기 위해서는

쌓아 올려지는 칩들을 서로 연결해주는 패키징이 가장 핵심적인 부분이 되겠습니다.

여기에 있는 TSV라는 단어.

앞으로 기억해 둘 만한 단어가 되겠습니다.

이렇게 수직으로 쌓인 칩들의 상단과 하단을 연결해내는 기술입니다.

물론 기존에도 수직으로 칩들을 적층 해내는 방법이 있었습니다.

대표적인 것이 Wire Bonding입니다.

기존의 방식인 이 Wire Bonding과 Through Silicon Via 둘 간의 차이가 눈에 들어오시나요?

WB의 경우 외부적인 연결통로를 만들어 전극을 통해 각각의 층들을 연결하는 것이고

TSV는 이 TSV를 이루는 단어들이 의미하는 바 대로 층들을 관통하는 미세홀을 뚫고

내부에 전도성 물질들을 충전해 층층이 쌓인 칩들을 연결하는 방법으로

TSV를 통해 기존의 WB에 비해 물리적으로도 칩 간의 더 많은 채널이 확보되고 더 높은 대역폭과

더 빠른 속도의 유기적인 연결을 구현합니다.

따라서 HBM이라는 이름은 바로 이 구조가 가진 장점 중 하나를 강조한 그런 네이밍이 되겠습니다.

하지만 해당 이름 안에 너무 매몰되게 되면 이 구조가 갖는 진짜 의미를 지나치게 될 수도 있습니다.

TSV로 D램 칩들이 층층이 연결된 모습은 단순히 램의 대역폭을 넓히는 것을 넘어

X와 Y축으로 이루어진 네모난 공간의 한계를 넘어 발전을 이어가는 메모리 반도체의

Z에 대한 이야기가 되겠습니다.

그리고 이 반도체 시장의 Z는 단지 메모리 영역에만 국한된 이야기는 아닙니다.

이제 로직 반도체의 Z에 대한 이야기를 나눠보면 좋겠습니다.

< 로직 반도체 시장의 Z >

로직 반도체를 대표하는 분야 중 하나인 GPU 시장에도 앞서 이야기 나눈 HBM이 적용되어

제품 성능의 발전을 이어나가고 있습니다.

GPU 시장의 최초에 HBM 적용은 AMD의 Fiji 아키텍처입니다.

해당 아키텍처를 사용한 모델 중 대표적인 것이 AMD의 라데온 R9 Fury가 되겠습니다.

HBM이 적용된 보다 진보된 설계가 계속 다듬어져

최근에 Vega 아키텍처까지 이어오게 된 것입니다.

이렇게 HBM을 적용한 새로운 GPU 설계 구조 덕에

GPU와 램간의 물리적인 거리가 줄어들고 더 넓은 대역폭의

보다 빠른 연산이 가능해졌습니다.

그런데 또 한 가지 빠지면 섭섭한 시장이 있습니다.

바로 로직 반도체의 꽃이라고 할 수 있는 CPU 시장입니다.

이렇게 CPU와 함께 GPU나 여러 가지 칩들을 함께 넣게 되면

이것을 '시스템 온 칩'이라고 합니다.

여기서 한 발자국 더 나아가 각각의 다이들을 적층 하게 되면

3D CPU 구조가 탄생하게 됩니다.

올 초 CES에서 인텔이 공개했던 레이크필드가 있습니다.

우선 하나의 Big CPU와 4개의 Small CPU로 구성된 하이브리드 CPU구조가 눈에 띕니다.

앞서 이야기 나눈 '시스템 온 칩'의 개념이 되겠습니다.

여기에 HBM 적층 구조의 D램 다이, 캐시와 I/O 다이가 함께 적층 되면

인텔 진영에서는 '포베 로스(FOVEROS)'라는 코드 네임을 붙인

이 3D CPU 구조가 탄생합니다.

이곳에서도 역시 익숙한 단어가 보입니다.

이 TSV를 통해 HBM뿐만 아니라 서로 다른 종류들의 다이들이 유기적으로 연결된

적층 구조과 완성되고 또 한 가지 중요한 이름이 나옵니다.

바로 Interposer가 되겠습니다.

이렇게 서로 다른 칩들로 구성된 다이들이

Inerposer를 통해 연결이 되어있는데

앞으로 더 많은 기능, 더 강력한 컴퓨팅 파워를 갖춘 아키텍처가

바로 TSV와 Inerposer로 칩들 간의 유기적으로 연결되어 있는

3D 적층 구조, 바로 반도체 시장의 Z 속에서 탄생하게 되었습니다.

계속해서 발전해가는 반도체 시장의 기술력은

우리나라뿐만 아니라 더 나은 인류의 발전을 위해

아주 필수적인 요소라고 생각합니다.

이제는 반도체 시장의 기술 한계다 라고 하는 순간마다

코웃음 치며 발전된 신기술을 보이는 모습들이

정말 감명 깊습니다.

긴 글 읽어주셔서 감사합니다.

좋은 하루 보내세요.

'IT's > Story' 카테고리의 다른 글

| 삼성전자, 에어팟을 이길 수 있을까 - 버즈빈VS에어팟 프로 라이트 (0) | 2020.05.07 |

|---|---|

| SMIC, 중국 1위 반도체 파운드리 기업-양몽송,14나노 공정 (0) | 2020.05.03 |

| SMIC, 중국의 파운드리 시장 욕심 - SMIC 반도체 기업에 대해서(1) (0) | 2019.09.04 |

| 반도체의 Z에 대한 이야기 - D램 시장과 기술 한계 극복(1) (0) | 2019.08.31 |

| 미중 무역 전쟁에 맞선 화웨이의 하모니OS(2) - 안드로이드 발전과정과 훙멍OS의 한계 (0) | 2019.08.22 |